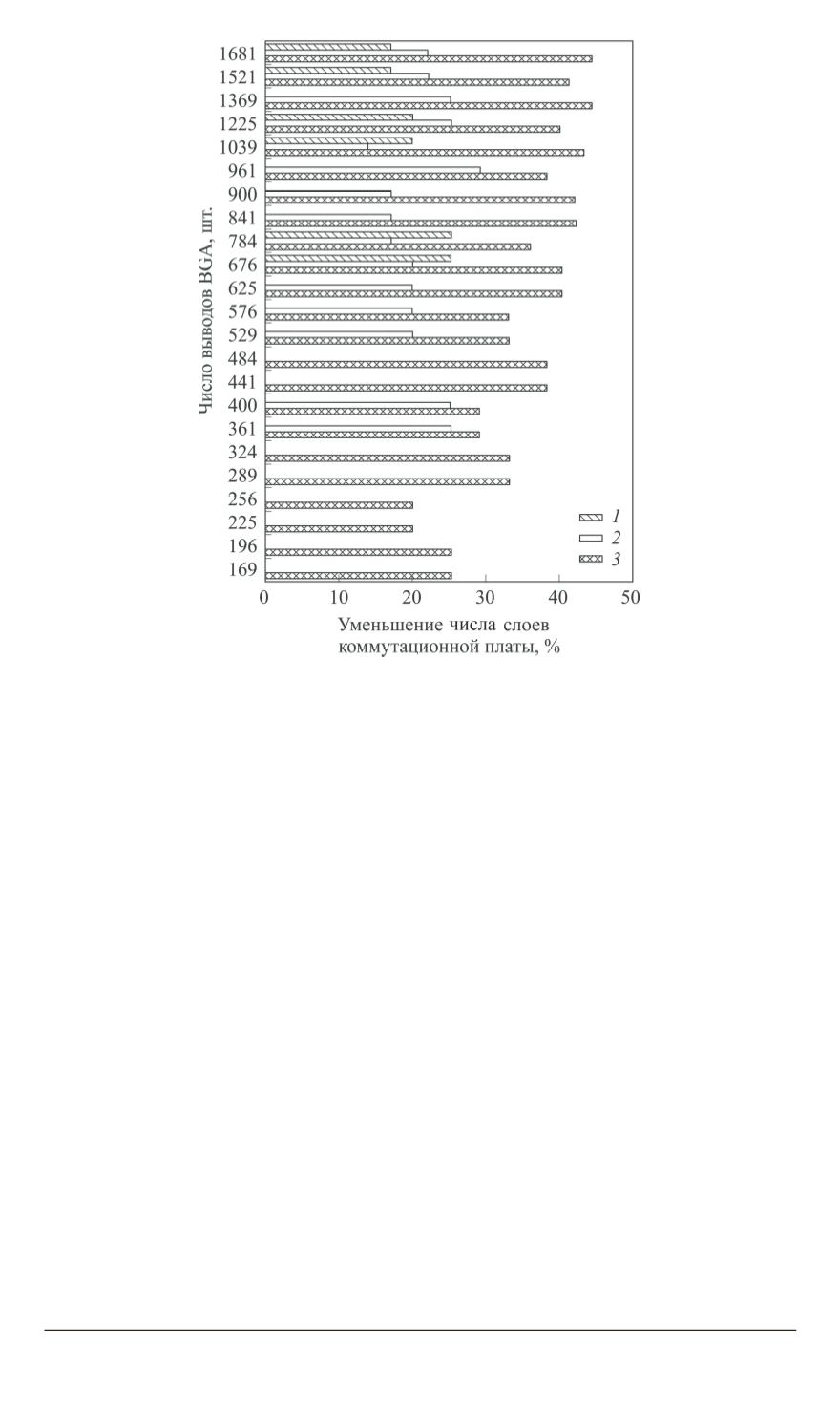

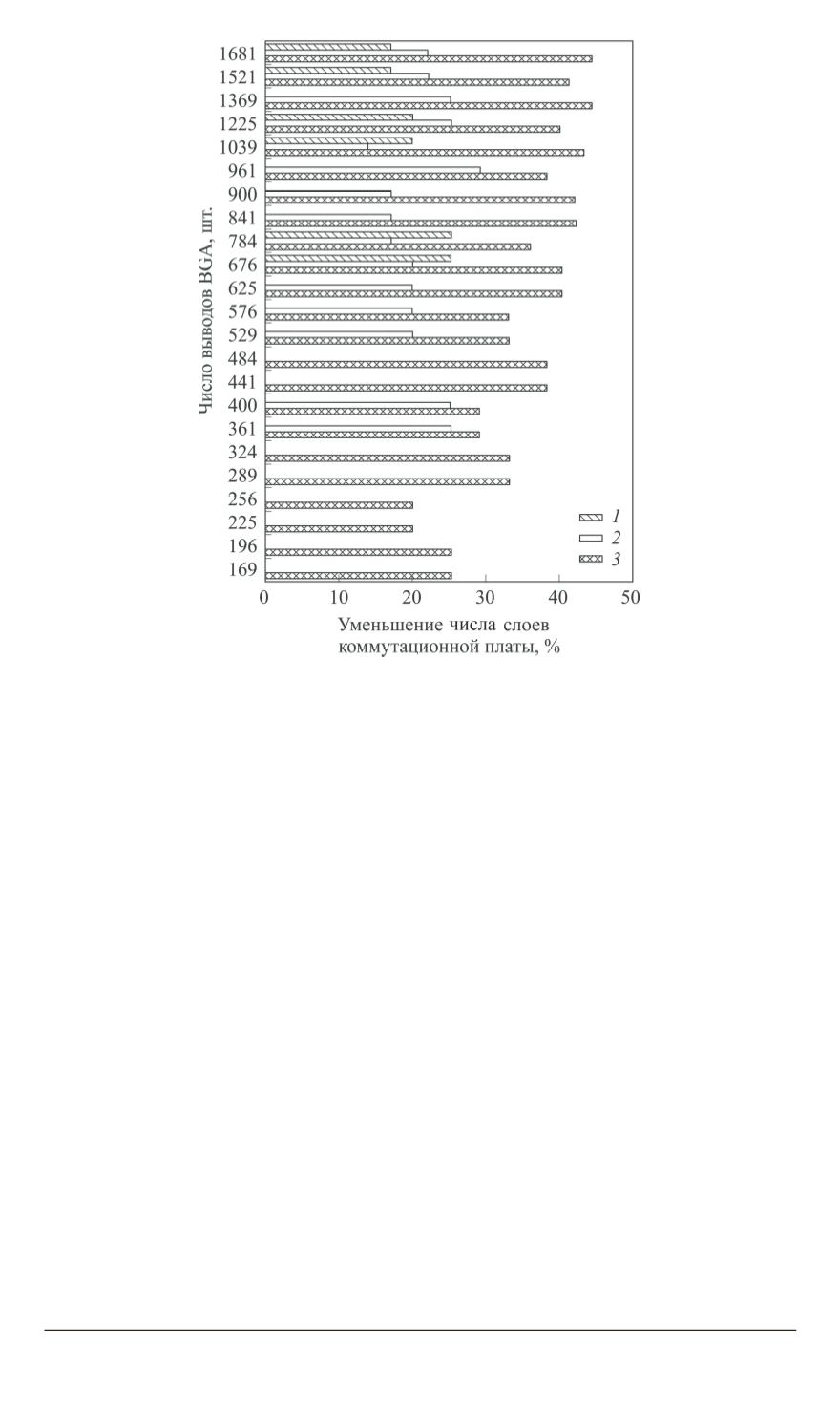

Рис. 5. Уменьшение числа слоев коммутационной платы ЗГП, предназначенной

для трассировки BGA-компонента, относительно платы МСО:

1

,

2

и

3

—

n

= 1

, 2 и 3 соответственно

до 2,4 раз и уменьшать число слоев коммутационной платы до 44%

относительно традиционного решения МСО.

ЛИТЕРАТУРА

1.

Кумбз К.Ф.

Печатные платы: Справочник. В 2 кн. Кн. 1 / пер. с англ. М.: Тех-

носфера, 2011. 1016 с.

2.

IPC-7095 Design

and assembly process implementation for BGAs — Association

connecting electronics industries, 2003. 88 p.

3.

SPRU811A Flip

chip ball grid array package reference guide — Texas Instruments,

2005. 71 p.

4.

UG112 Device

package user guide — XILINX, 2009. 118 p.

5.

Нинг-Ченг Ли.

Технология пайки оплавлением, поиск и устранение дефектов:

поверхностный монтаж, BGA, CSP и Flip chip технологии / пер. с англ. М.:

Технологии, 2006. 392 с.

6.

IPC-A-610 Acceptability

of electronic assemblies — Association connecting

electronics industries, 2004. 390 p.

7.

ГОСТ Р 53429–2009

“Платы печатные. Основные параметры конструкции”. М.:

Стандартинформ, 2010. 11 с.

8.

Миронова Ж.А.

,

Шахнов В.А.

,

Гриднев В.Н.

Высокоплотная компоновка меж-

соединений многослойных коммутационных плат: XVI Молодеж. Междунар.

науч.-техн. конф. “Наукоемкие технологии и интеллектуальные системы”. М.:

МГТУ им. Н.Э. Баумана, 2014. С. 213–218.

68 ISSN 0236-3933. Вестник МГТУ им. Н.Э. Баумана. Сер. “Приборостроение”. 2014. № 6