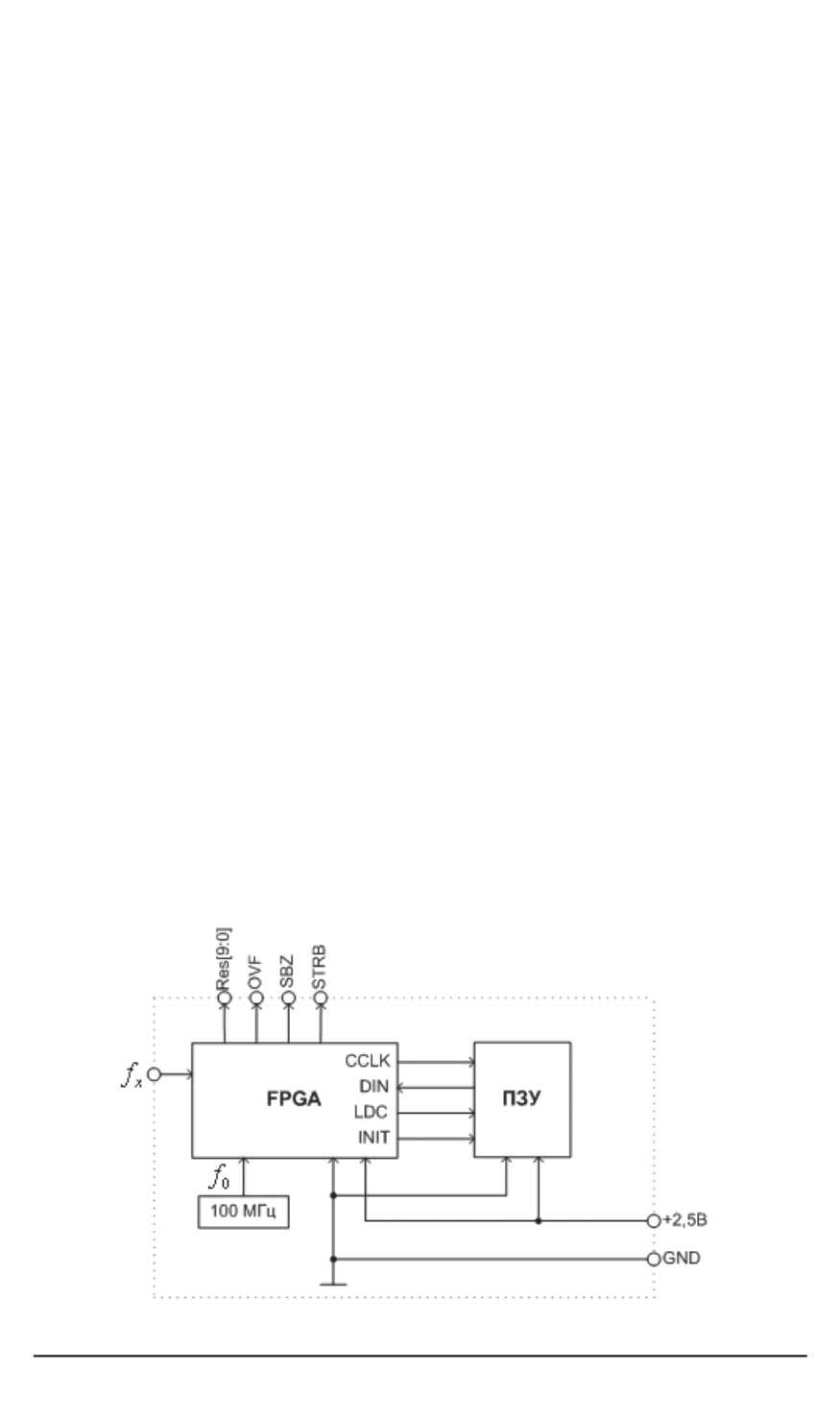

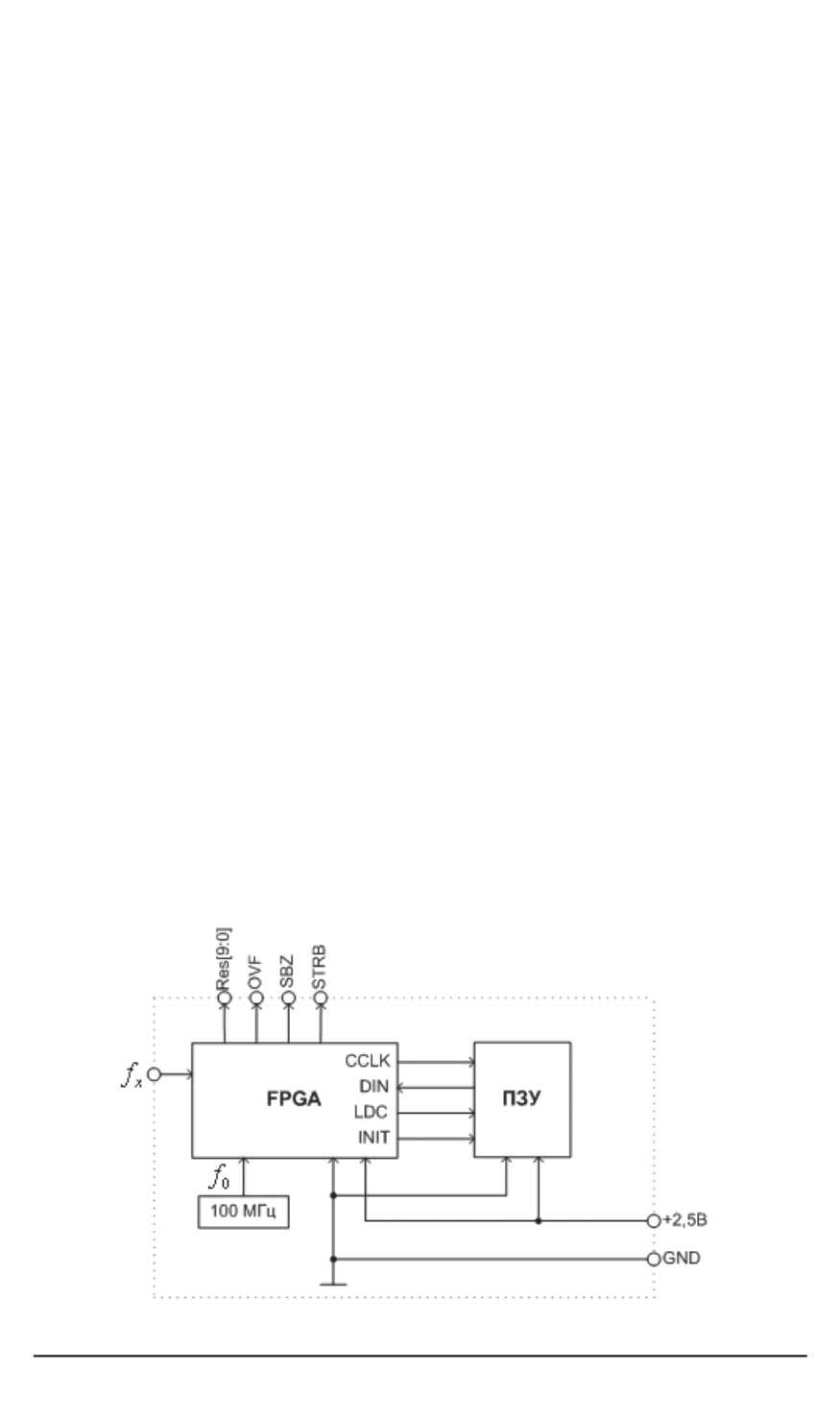

FPGA XC2S15–5VQ100C фирмы Xilinx емкостью 15 тыс. эквивалент-

ных вентилей. В качестве постоянного запоминающего устройства

(ПЗУ) для хранения кодов соединений (прошивки) применяется ми-

кросхема XC17S15XLPD8C — последовательное ПЗУ, специально

разработанное под этот кристалл. Оба используемых чипа работают

при напряжении питания 2,5 В, что обеспечивает низкую потребляе-

мую ими мощность. В качестве генератора синхросигналов с частотой

f

0

= 100

МГц применяется микросхема НО-11С-100.000.

Стоимость комплектующих:

XC2S15–5VQ100C ( микросхема FPGA) — 6,8 долл.,

ХС17S15XLPD8C (ПЗУ) — 2,1 долл.,

НО-ПС-100.000 (БИС генератора) — 2,5 долл.

Синаптические связи ИНС преобразователя в выбранной микро-

схеме ПЛИС реализованы при помощи двоичных умножителей часто-

ты [1]. При применении более дорогих микросхем ПЛИС (с ценой от

12 долл. и выше) они могут быть реализованы на основе цифровых

менеджеров частот (DCM).

На принципиальной схеме устройства (рис. 4) использованы сле-

дующие обозначения:

f

x

— сигнал с частотного датчика; Res[9:0] —

выход результата

y

∗

n

в виде 10-разрядного унитарного кода; STRB —

строб выдачи

y

∗

n

;

f

0

=

f

x

max

— опорная частота преобразования; OVF

и SBZ — индикация значений переменной

h

биосигнала, например

больше и меньше максимально допустимых.

После включения питания кристалл FPGA автоматически загружа-

ет в себя программу из ПЗУ и начинает функционировать в соответ-

ствии с работой электрической схемы ИНС-преобразователя, создан-

ной (скомпилированной) при помощи специальной системы автомати-

зированного проектирования (САПР). При разработке схемы реализо-

ваны такие ее возможности, как построение иерархических структур,

Рис. 4. Принципиальная схема ИНС-преобразователя сигналов на базе FPGA

ISSN 0236-3933. Вестник МГТУ им. Н.Э. Баумана. Сер. “Приборостроение”. 2009. № 3 87