Рис. 3. Логическая схема второго слоя трехразрядного ИНС-преобразователя

f

x

→

N

y

на основематриц

W

(2)4

(38) и

Θ

(2)4

(39)

учетом знака

w

(2)7

j,i

=

⎧⎪⎪⎨

⎪⎪⎩

1

,

если

w

(2)6

j,i

>

1

,

−

1

,

если

w

(2)6

j,i

<

−

1

,

w

(2)6

j,i

иначе

.

j

= [ 1

, k

]

, i

= [ 1

, k

]

,

(43)

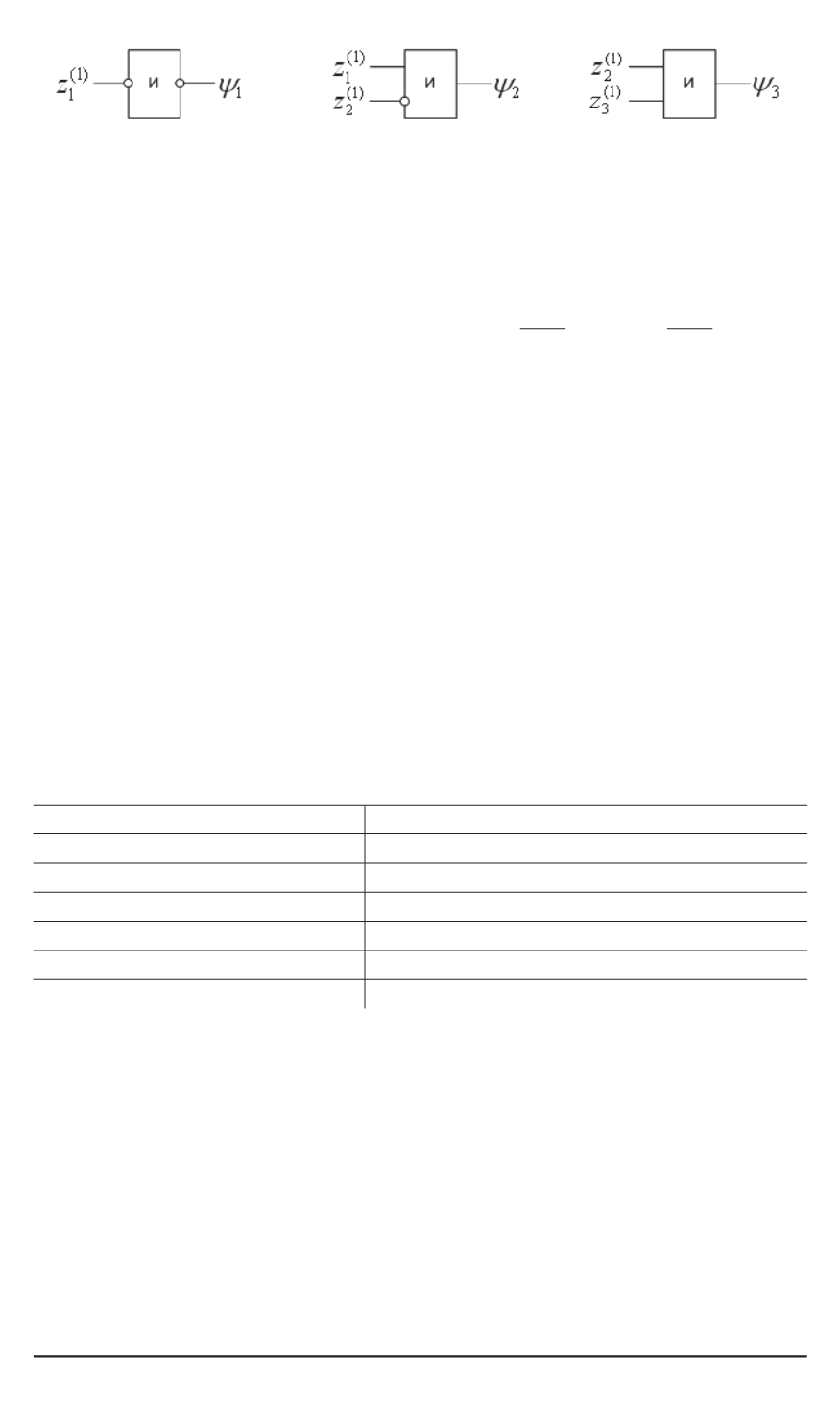

С учетом проведенной процедуры коррекции логическая схема,

реализующая второй слой двухслойного персептрона трехразрядного

ПФИ

f

x

→

N

y

(см. рис. 1) с использованием значений весов (38) и

порогов (39), содержит только двухвходовые логические элементы “И”

(рис. 3) вместо цифровых умножителей (см. рис. 2).

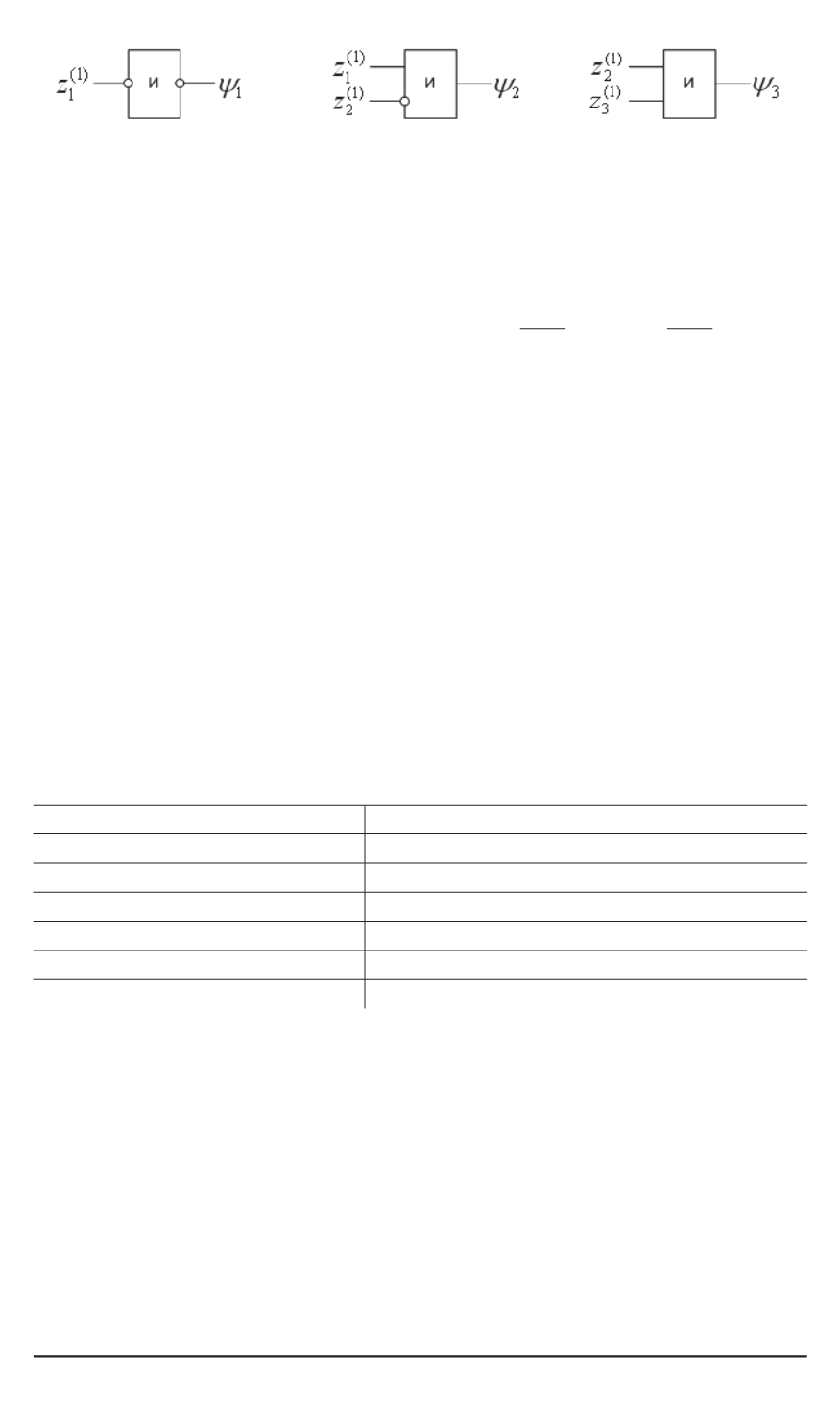

В таблице приведены характеристики аппаратных затрат

C

(2)

на

реализацию второго слоя сети ПФИ

f

x

→

N

y

(см. рис. 1) на основе

схем, представленных на рис. 2 и 3, в зависимости от числа

k

разрядов

(разрядности) результата

N

y

для нескорректированных и скорректиро-

ванных весов синаптических связей и порогов нейронов.

Таблица

Зависимость аппаратных затрат

C

(2)

второго слоя ПФИ

f

x

→

N

y

от

разрядности

k

результата

N

y

Разрядность

k

результата

N

y

LUT (до / после коррекции)

3

168 / 3

4

288 / 4

6

624 / 6

8

1088 / 8

10

1680 / 10

12

2400 / 12

Как видно из таблицы, реализация второго слоя сети ПФИ

f

x

→

N

y

на логических элементах с использованием скорректированных значе-

ний весовых коэффициентов и порогов нейронов позволяет на два

порядка сократить аппаратные затраты по сравнению с применени-

ем весовых коэффициентов, полученных на основе настройки сети с

использованием алгоритма обратного распространения ошибки [11].

Реализация структуры ИНС-преобразователя частоты

f

x

в

код

N

y

на основе двухслойного персептрона.

При микроэлектрон-

ной реализации структуры ИНС-преобразователя (см. рис. 2) с учетом

скорректированных значений весовых коэффициентов и порогов ней-

ронов на основе описанных ранее процедур использована микросхема

86 ISSN 0236-3933. Вестник МГТУ им. Н.Э. Баумана. Сер. “Приборостроение”. 2009. № 3