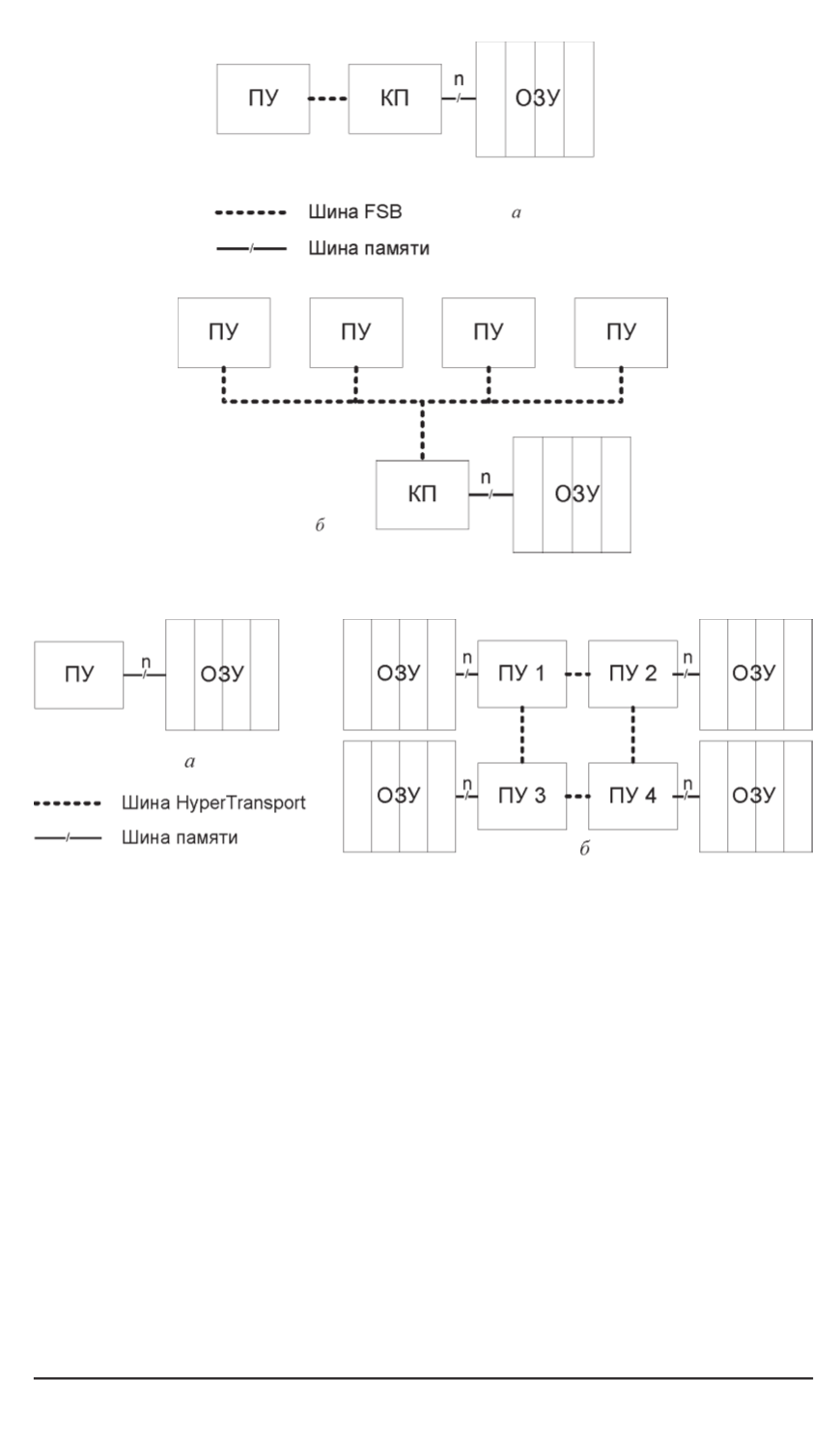

Рис. 1. Типовая схема организации доступа к ОЗУ Intel Pentium4 (

a

) иIntel

Xeon (

б

)

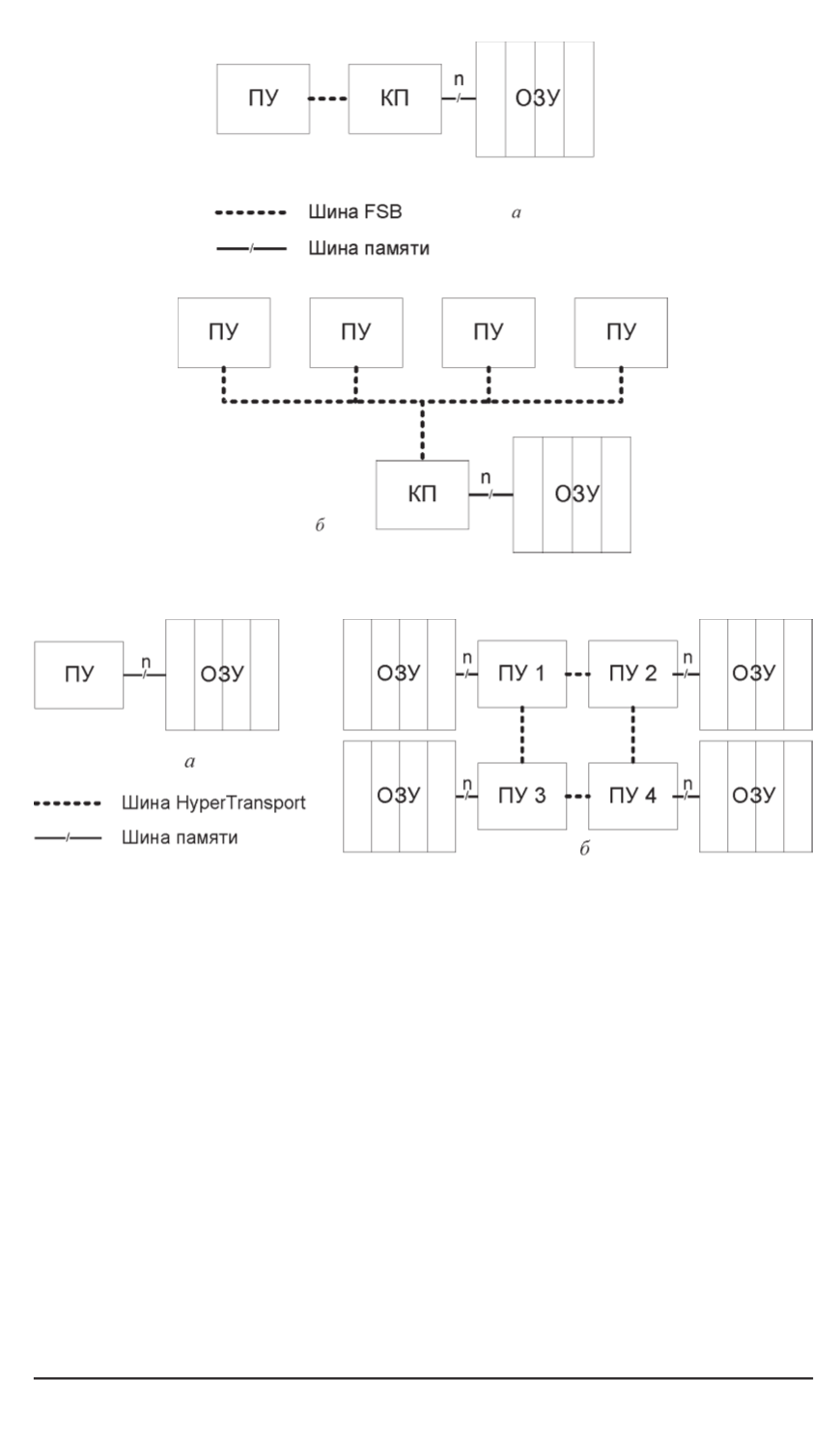

Рис. 2. Типовая схема доступа к ОЗУ AMD Athlon 64 (

a

) иAMD Opteron (

б

)

с отдельными процессорными узлами не предусмотрена, однако, воз-

можность использования многоядерного процессорного узла требует

оценки снижения общей производительности при параллельной ра-

боте нескольких ядер. Данная архитектура отличается от архитектуры

Intel отсутствием шины процессора. Соответственно, модель принима-

ет следующие параметры: k

2

k

1

,

SY S

RS

= [1]

,

SY S

ex

= 0 0 1

,

act

cpubus

= 0 0

,

act

membus

= 1 0

.

Модель архитектуры AMD Opteron x4.

К сожалению, в связи с

отсутствием регулярности построения многопроцессорных ВС дан-

ной архитектуры, создание обобщенной модели затруднено. Рассмо-

трим модель, содержащую 4 процессорных узла, соединенных шина-

ми HyperTransport по кругу (см. рис. 2).

Модель состоит из процессов, описывающих обращения каждого

процессора ко всем возможным ОЗУ. Индекс процесса соответствует

ISSN 0236-3933. Вестник МГТУ им. Н.Э. Баумана. Сер. “Приборостроение”. 2007. № 3 97