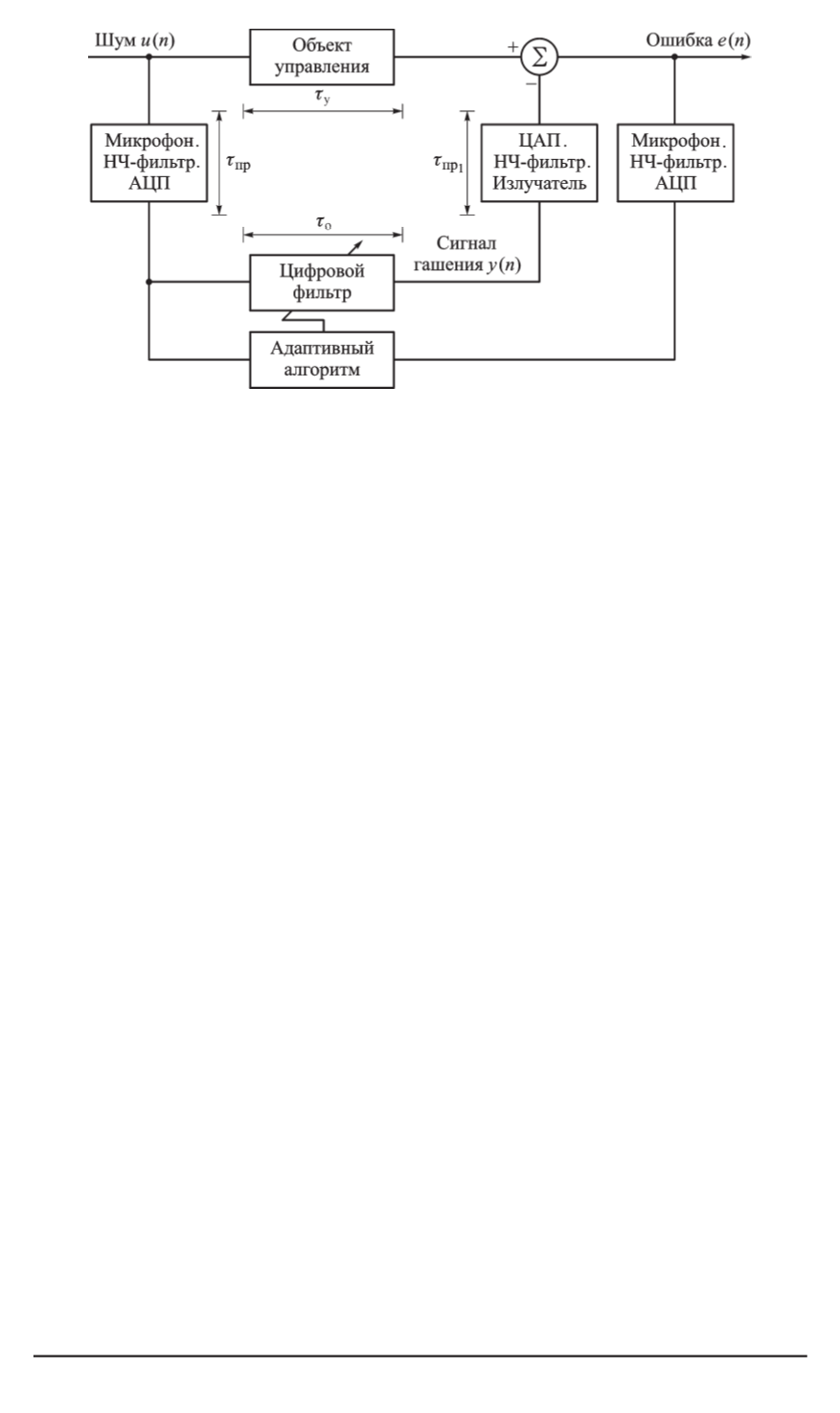

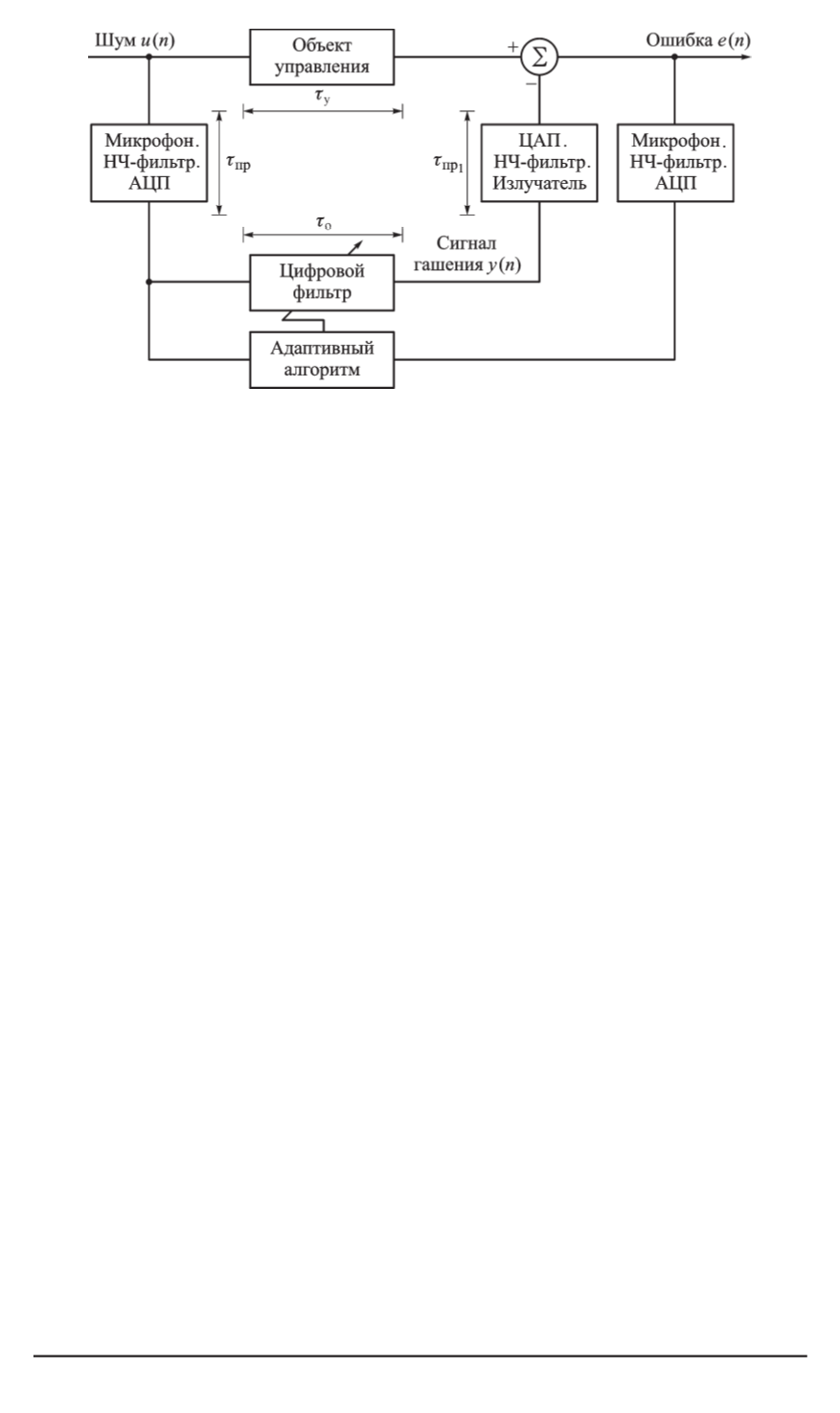

Рис. 6. Распределение задержек сигнала в обобщенной модели САГ

ки сигнала, вносимые блоком управления, определяются производи-

тельностью используемыхсредств цифровой обработки и вычисли-

тельными требованиями алгоритмов. Если производительность аппа-

ратныхвычислительныхсредств напрямую зависит от достигнутого

при ихпроизводстве технологического уровня, то выбор техили иных

алгоритмов является многокритериальной задачей и требует проведе-

ния всестороннего анализа. Используя упрощенные алгоритмы, мож-

но уменьшить задержки, но увеличить время сходимости или снизить

качество гашения.

С помощью созданныхв среде MATLAB моделей оценим вноси-

мые обоими типами преобразователей задержки. Для этого подадим

на ихвходы последовательность прямоугольныхимпульсов с частотой

следования 700 Гц. Результат преобразования можно контролировать

на экране виртуального осциллографа (рис. 7, 8).

Результаты моделирования показывают, что преобразователи па-

раллельного типа имеют существенно меньшее время преобразования

по сравнению с сигма-дельта преобразователями. Если для параллель-

ныхпреобразователей время преобразования не превышает одного

отсчета, то для сигма-дельта преобразователя оно составляет около

100 мкс. Это подтверждается и экспериментально — для сигма-дельта

АЦП при тактовой частоте 32 кГц задержка составляет около 4 отсче-

тов, т.е. 125 мкс. Это значение определяется помимо тактовой частоты

одноразрядного преобразователя, также и порядком НЧ-фильтра в бло-

ке децимации.

Что касается числа эффективныхразрядов, определяемого экспе-

риментально из соотношения сигнал/шум преобразователя, то здесь,

если не принимать во внимание элементы обвязки, на первый план вы-

ходят три составляющие (рис. 9): шумы квантования, интермодуляция

и джиттер.

ISSN 0236-3933. Вестник МГТУ им. Н.Э. Баумана. Сер. “Приборостроение”. 2008. № 4 95