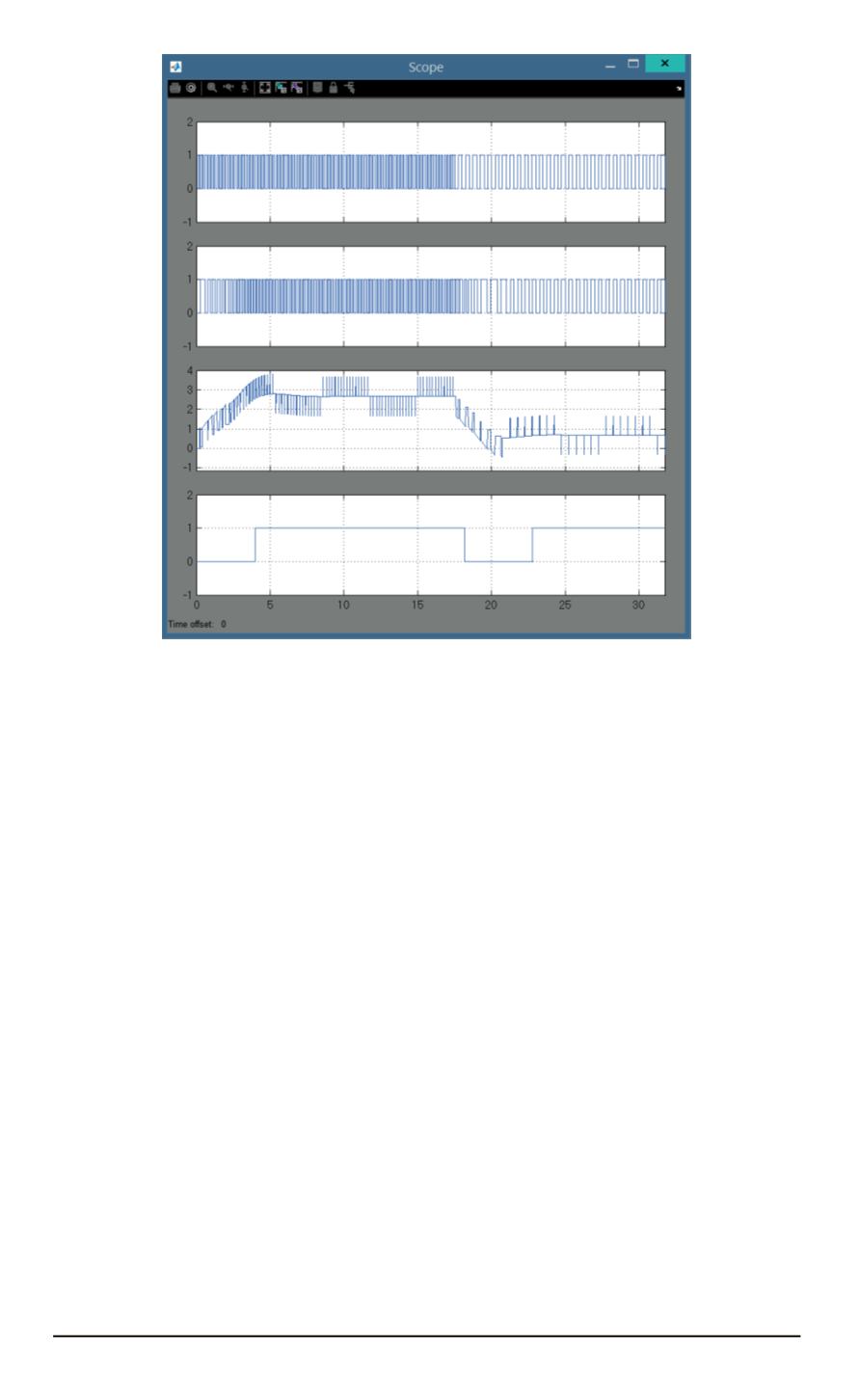

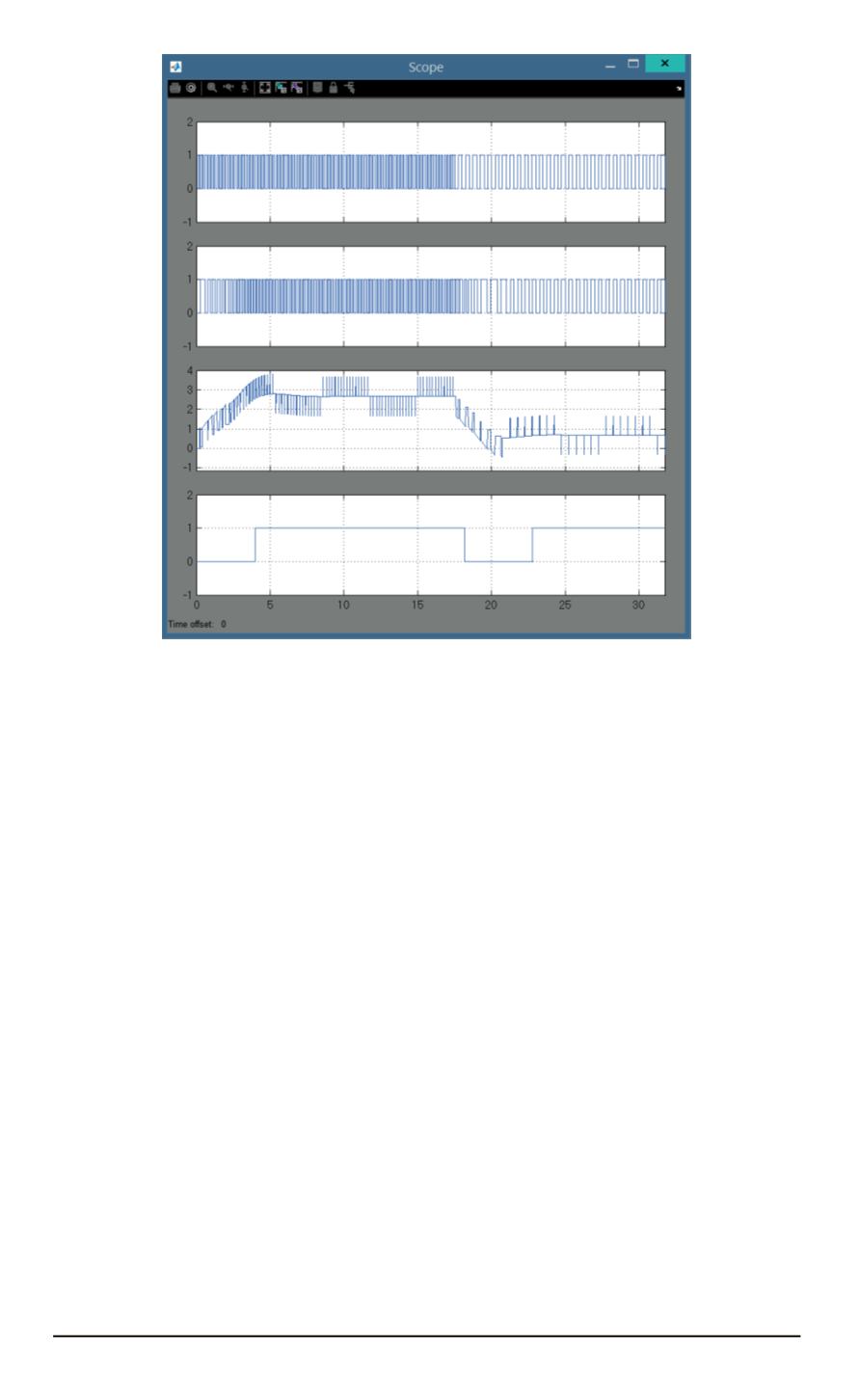

Рис. 6. Результаты моделирования переходного процесса после включения схе-

мы и дальнейшей перестройки частоты опорного генератора (Ref, Feedback,

Control, Lock)

сигналов, формируемых устройствами на основе ФАП, а также отно-

сительная сложность схемной реализации, сравнимая со сложностью

самого ЧФД.

ЛИТЕРАТУРА

1.

Floyd M.G.

Charge-Pump Phase-Lock Loops // IEEE Transaction On

Communications. Vol. COM-28. No. 11. November 1980.

2.

Floyd M.G.

Phase-lock Techniques. New Jersey: John Wiley & Sons, Inc. Hoboken,

2005. 450 p.

3.

Vowe A.Dr.

Patent EP 0878912 B1. Lock detector circuit for a phase locked loop.

2003.

4.

Kallman K.A.

,

Blanchard S.D.

,

Bucher W.A.

Patent US 5694440 A. Data synchronizer

lock detector and method of operation thereof. 1997.

5.

Levine S.N.

Patent US 4617520 A. Digital lock detector for a phase-locked loop.

1986.

6.

Wu Kuang Tsan

,

Sun Han

,

McNicol J.

Patent US 7292653 B2. Carrier lock detector.

2007.

7.

Markman I.

,

Edde G.A.

Patent US 7421042 B2. Carrier tracking loop lock detector.

2008.

8.

Patent

US 6879195 B2. PLL lock detection circuit using edge detection / M. Green,

N.M. Nguyen, Y. Frans, D. Kim, T. Bystrom. 2005.

9.

Bui M.M.

,

Potemski A.S.

Patent US 5126690 A. Phase locked loop lock detector

including loss of lock and gain of lock detectors. 1992.

ISSN 0236-3933. Вестник МГТУ им. Н.Э. Баумана. Сер. “Приборостроение”. 2014. № 5 75